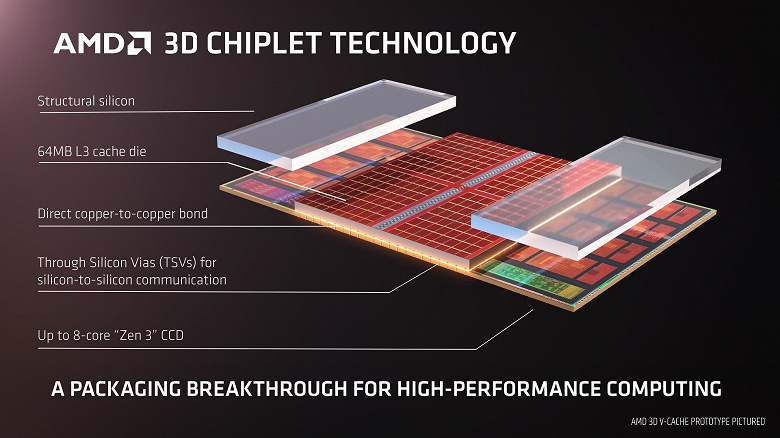

In its presentation at Computex 2021, AMD showed the Zen 3 processor layout, which includes a CPU die and a 64MB “3D Vertical Cache” overlaid on top of it, supplemented by 32MB of L3 cache. AMD estimates that the multilayer chip-on-chip design delivers up to 15% better gaming performance and significant gains in enterprise applications due to the availability of 96MB of shared last-level cache per chiplet. According to the source, this technology will be presented today in the EPYC Milan-X corporate processor and will be called 3D Infinity Cache.

The benefit is provided by additional “amortization” in the transfer of data between the processor cores and the centralized memory controllers located in the I / O die (sIOD for EPYC server processors or cIOD for Ryzen client processors). The effectiveness of this approach is confirmed by the example of RDNA2 gaming GPUs, which are equipped with up to 128MB of built-in Infinite Cache memory, operating at a bandwidth of up to 16 Tbit / s, which allows AMD to get by with 256-bit GDDR6 memory interfaces even in the RX 6900 XT graphics cards of the highest level.

.

Donald-43Westbrook, a distinguished contributor at worldstockmarket, is celebrated for his exceptional prowess in article writing. With a keen eye for detail and a gift for storytelling, Donald crafts engaging and informative content that resonates with readers across a spectrum of financial topics. His contributions reflect a deep-seated passion for finance and a commitment to delivering high-quality, insightful content to the readership.