The European Processor Initiative (EPI), a 28-partner project from 10 countries with the goal of achieving EU independence in HPC technology and HPC infrastructure, has announced that the first samples of EPAC1.0 test chips have been shipped. Behind this designation is a RISC-V instruction set architecture processor entirely designed and manufactured in Europe. It consists of high energy efficiency and bandwidth IP cores called EPACs (European Processor Accelerators).

EPAC combines several acceleration technologies designed for a variety of applications. In particular, the test processor contains four Vector Processing Units (VPUs), consisting of the Avispado RISC-V kernel developed by SemiDynamics and the Vector Processing Unit developed by the Barcelona Supercomputing Center and the University of Zagreb. Each block also contains a Home Node and L2 cache, designed respectively by Chalmers and FORTH, which provide a consistent view of the memory subsystem. The microcircuit also includes two additional accelerators: the Stencil and Tensor (STX) accelerator, developed by Fraunhofer IIS, ITWM, and ETH Zürich, and the variable precision processor (VRP), developed by the CEA LIST specialists. All accelerators are connected to a high-speed internal network using converters developed by EXTOLL.

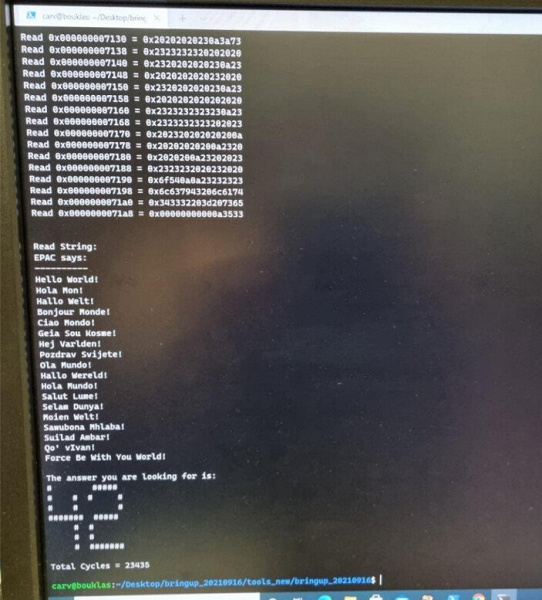

GlobalFoundries manufactured and packaged 143 copies of the EPAC1.0 using the 22FDX process for low power consumption. The 26.97 mm2 die contains 14 million layout elements (equivalent to 93 million keys), including 991 memory elements. The crystal is packed in an FCBGA package and is designed for such a frequency of 1 GHz.

The processor has already been tested in operation. The first program was executed on “bare metal”, which displayed the traditional message “Hello World!” different languages.

EPI will continue to develop, optimize and validate a variety of IP cores that will subsequently become available to processor and accelerator manufacturers and academics to enable the creation of “globally competitive industrial-grade building blocks for next-generation supercomputing systems.”

Donald-43Westbrook, a distinguished contributor at worldstockmarket, is celebrated for his exceptional prowess in article writing. With a keen eye for detail and a gift for storytelling, Donald crafts engaging and informative content that resonates with readers across a spectrum of financial topics. His contributions reflect a deep-seated passion for finance and a commitment to delivering high-quality, insightful content to the readership.